https://doi.org/10.33180/InfMIDEM2020.302

Informacije MIDEM

Journal of Microelectronics, Electronic Components and Materials Vol. 50, No. 3(2020), 169 – 177

# Superior Performance of a Negative-capacitance Double-gate Junctionless Field-effect Transistor with Additional Source-drain Doping

Zhifeng Zhao, Tianyu Yu, Peng Si, Kai Zhang, Weifeng Lü

Hangzhou Dianzi University, Key Laboratory for RF Circuits and Systems of Ministry of Education, Hangzhou, China

**Abstract:** In this work, we propose a negative-capacitance double-gate junctionless field-effect transistor (NC-JLFET) with additional source-drain doping. Superior performance of the NC-JLFET due to source and drain doping concentration is explained in detail. Additionally, the effects of the drain induced barrier lowering (DIBL) and negative differential resistance (NDR) are precisely analyzed in the NC-JLFET. Sentaurus TCAD simulation demonstrates that the additional source-drain-doped NC-JLFET exhibits a higher on/ off current ratio (ION/IOFF) and steeper subthreshold swing (SS < 60 mV/dec) compared to a traditional JLFET. Besides, the negative capacitance effect causes the internal voltage of the gate to be amplified, resulting in negative DIBL and NDR phenomena. Finally, the performance of NC-JLFET can also be optimized by choosing suitable ferroelectric material parameters, such as ferroelectric thickness, coercive field, and remnant polarization. Our simulation study provides theoretical and experimental support for further performance improvement of low-power NCFETs by local structure adjustment.

**Keywords:** Negative-capacitance double-gate junctionless field-effect transistor; additional source-drain doping; on/off current ratio; subthreshold swing; drain induced barrier lowering

# Odlična učinkovitost dvovratnega brezspojnega poljskega tranzistorja z negativno kapacitivnostjo z dodatnim dopiranjem izvor-ponor

Izvleček: V članku je predlagan dvovratni brezspojni poljski tranzistor z negativno kapacitivnostjo z dodatnim dopiranjem izvor-ponor (NC\_JLFET). Natančno je predstavljena odlična učinkovitost NC\_JLFET zaradi dodatnega dopiranja izvora in ponora. Analizirano je znižanje bariere (DIBL) zaradi ponora in negativna diferencialna rezistivnost (NDR). Sentaurus TCAD simulacije kažejo, da dodatno dopiranje izvora in ponora vodi v višjo tokovno razmerje (ION/IOFF) in strmejši podpragovni nihaj (SS< 60 mV/dec). Negativna kapacitivnost povzroča ojačenje notranje napetosti vrat, ki se izkazuje v negativni DIBL in NDR efektu. Učinkovitost NC-JLFET je lahko optimiziran s pravilnimi parametri feroelektričnega materiala, kot je debelina, prisilno polje in preostale polarizacije. Simulacije ponujajo teoretično in eksperimentalno pomoč pri optimizaciji NCFET tranzistorja nizkih moči.

Ključne besede: dvovratni brezspojen poljski tranzistor z negativno kapacitivnostjo; dopiranje izvor-ponor; on/off tokovno razmerje; podpragovni nihaj; znižanje bariere

\* Corresponding Author's e-mail: lvwf@hdu.edu.cn

# 1 Introduction

With the continuous development of integrated circuits (ICs), device sizes have been gradually shrinking. The performance of traditional metal-oxide-semiconductor field-effect transistors is approaching its limit. The off-state leakage current is increasing exponentially caused by the short-channel effect (SCE), resulting in unacceptable static power [1]. At the same time, it has become difficult for inversion-mode field effect transistors (FETs) (IMFETs) to achieve ultra-deep doping concentration gradients at the device junctions, inducing increasing thermal budget [2]. To overcome these obstacles, some novel device structures have been proposed, including junctionless FETs (JLFETs) and ferroelectric negative-capacitance FETs (NCFETs) [3]-[5].

Compared with traditional inversion-mode transistors, JLFETs have stronger immunity to the SCE [6]. In the actual manufacturing process, there is no super-steep junction, and no additional dopants must be injected into the source and drain regions because the source and drain have the same doping polarity and concentration as the channel. Thus, JLFETs have a simpler manufacturing process and a lower thermal budget than IM-FETs [7]. In JLFETs, the majority carriers are conducted in the center of the channel instead of the surface, and the majority carriers in the channel are completely depleted by the gate bias to shut down the device. Moreover, the multigate structure can effectively improve the gate-tochannel control capability, so JLFET devices usually use a double gate to achieve complete channel depletion [8]. It has been verified that the gate metal of JLFETs must have a work function greater than 5.0 eV to completely deplete the Si body to reach the off state [2]. However, it is difficult for a gate metal with a relatively large work function to meet the thermal stability requirement and achieve good adhesion to the gate dielectric [7]-[9]. Therefore, a novel mechanism or structure must be found to overcome this problem.

Since the NCFET was first proposed [4], there have been many reports on both IM and JL structures. A new transistor concept is proposed that combines ultra-thin body and NCFET in [10], It has been proved that performance improvement with low-power NCFETs is realized by amplifying the internal gate voltage caused by the negative-capacitance effect. Hu et al. studied the effects of the variation of ferroelectric material properties (thickness, polarization, and coercivity) on the performance of negative capacitance FETs (NCFETs) in [11]. In our previous studies, we discussed the capacitance matching problem caused by the change of ferroelectric parameters in IM devices, and the performance of NCFET in RF applications [12,13]. Yejoo Choi studied the electrical characteristics of NC-JL-NWFET based on HfO2 through TCAD and MATLAB simulations [14].

In addition, some studies have shown that additional source-drain doping  $(N_{s/D})$  of a JLFET can increase the on-state current, but it also causes the higher subthreshold swing (SS) and the drain induced barrier lowering (DIBL) effect to become more prominent [15,16]. NCFETs can achieve steep SS and improve the DIBL effect, while greatly reducing operating voltage and power con-

sumption [17]-[18]. Therefore, by combining the above two points, the advantages of NCFET can offset the negative effects brought by the additional source-drain doping of JLFET, which can make NC-JLFET have more excellent performance. However, the effect of structure adjustment, such as additional source-drain doping, on the performance of an NC-JLFET has not yet been understood. So, in this work, we construct an NC-JLFET by stacking ferroelectric layers on the gate of the baseline JLFET and investigate the influence of additional source-drain doping on its electrical characteristics. Using Sentaurus TCAD simulation, it is demonstrated that additional source-drain doped NC-JLFETs have improved performance over traditional JLFETs, such as higher  $I_{ON}/I_{OFFF}$  steeper SS, and negative DIBL.

### 2 Device Structure and Simulation

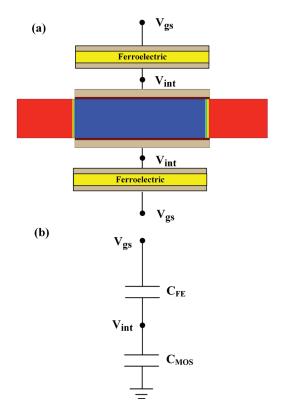

Figure 1a shows a two-dimensional diagram of an NC-JLFET using a metal-ferroelectric–metal-oxide–semiconductor (MFMIS) structure. The material of the insulating layer is SiO<sub>2</sub>; the channel, source, and drain are all N-type doped; source, drain, and channel. The channel is uniformly doped and the concentration remains fixed at  $1 \times 10^{19}$  cm<sup>-3</sup>. The source and drain are additionally doped with a concentration range of  $1 \times 10^{19}$  –  $5 \times 10^{19}$  cm<sup>-3</sup>.

**Figure. 1:** Schematic of (a) NC-JLFET and (b) capacitance equivalent model.

Table I lists other specific device parameters for the proposed NC-JLFET. Among them, the parameters of the baseline transistor JLFET are the gate length Lg=28nm, the silicon channel thickness W=10nm[14], and the metal work function WK is 5.0eV[2], these values of Pr and Ec are in the same range as those of ferroelectrics such as Hf- and Zr-based binary oxide ferroelectrics[11]. It is assumed that the inner and outer metals have the same work function and that the work function variation is not considered. Figure 1b is a schematic of the equivalent capacitance of the NC-JLFET, where  $C_{\text{FF}}$  is the ferroelectric layer capacitance and  $C_{MOS}$  is the gate equivalent capacitance of the baseline JLFET, including the insulation layer capacitance ( $C_{ox}$ ) and channel depletion capacitance ( $C_{dm}$ ). V<sub>gs</sub> and  $V_{int}$  are the external gate voltage and internal node voltage, respectively. The baseline JLFET is connected in series with the ferroelectric capacitor to form the NC-JLFET. The Landau-Khalatnikov (LK) equation with Gibbs free energy is the standard model of the ferroelectric capacitor, specifically described as the electric field in a ferroelectric as a function of polarization [19]:

$$E_{\rm FE} = 2\alpha P + 4\beta P^3 + 6\gamma P^5 + \rho \frac{dP}{dt}$$

(1)

where  $\alpha$ ,  $\beta$ , and  $\gamma$  are material-dependent parameters of the ferroelectric,  $\alpha = -3\sqrt{3}/4 \times E_{c}/P_{r}$ ,  $\beta = -3\sqrt{3}/8 \times E_{c}/P_{r}^{3}$ , and  $\gamma = 0$  [20], the values of which fit the parameter range in HfO<sub>2</sub>-based ferroelectrics [21]. The voltage across the ferroelectric capacitor can be obtained from:

$$V_{\rm FE} = \left(2\alpha P + 4\beta P^3 + 6\gamma P^5 + \rho \frac{dP}{dt}\right) \times T_{\rm FE}$$

(2)

Table 1: NC-JLFET device parameters

| Parameter       | Physical Meaning        | Value                  |

|-----------------|-------------------------|------------------------|

| Lg              | Gate length             | 28 nm                  |

| W               | Thickness of channel    | 10 nm                  |

| T <sub>ox</sub> | Oxide thickness         | 0.5 nm                 |

| T <sub>FE</sub> | Ferroelectric thickness | 1-5 nm                 |

| WK              | Metal work function     | 5.0 eV                 |

| E <sub>c</sub>  | Coercive field          | 1-1.2 MV/cm            |

| Pr              | Remnant polarization    | 3-5 µC/cm <sup>2</sup> |

Poisson's equation and the continuity equation are solved self-consistently with the LK equation at the same time using Sentaurus TCAD. In simulation, we used some physical models, including doping de-

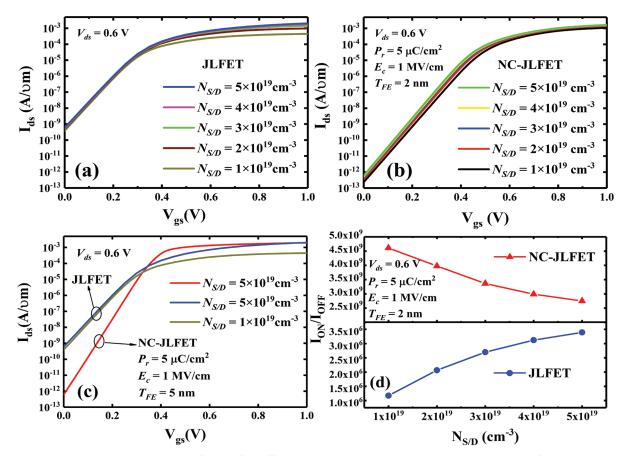

**Figure. 2:** (a) Transfer characteristics of JLFET for different source and drain doping concentrations of source and drain  $(N_{S/D})$ . (b) Transfer characteristics of NC-JLFET for different source and drain doping concentrations  $(N_{S/D})$ . (c) Transfer characteristics of NC-JLFET and JLFET. (d)  $I_{ON}/I_{OFF}$  with source and drain doping concentrations  $(N_{S/D})$ .

pendence, high-field saturation (velocity saturation) and considering the silicon bandgap narrowing, the old Slotboom model of band gap narrowing and the Shockley-Read-Hall model for recombination generation are also considered. In view of the highly doped source-drain regions, Fermi (also called Fermi–Dirac) statistics is necessary to make it more physically accurate. In addition, because the device dimension is very small, some quantum modification terms (eQuantum-Potential) are added for the simulation results to be closer to the real condition.

#### 3 Results and Discussion

Discussed herein are details of the effects of different source and drain doping concentrations  $(N_{s/D})$ , ferroelectric thickness  $(T_{FE})$ , and  $E_c$  and  $P_r$  values on the on/ off current ratio  $(I_{ON}/I_{OFF})$ , SS, DIBL, and output characteristics  $(I_{rts} - V_{rts})$ .

Figures 2a and b show the  $I_{ds}-V_{gs}$  transfer characteristics of JLFETs and NC-JLFETs with different  $N_{S/D}$  values, respectively. It is clear that, as  $N_{S/D}$  increases, the on current  $(I_{ON})$  increases more and the off current  $(I_{OFF})$  is al-

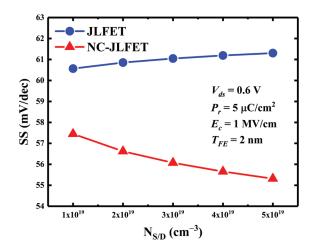

**Figure. 3:** Subthreshold swing (SS) of JLFET and NC-JLFET varying with source and drain doping concentration ( $N_{s(p)}$ ).

most constant in JLFETs, but  $I_{\rm ON}$  and  $I_{\rm OFF}$  both increase slightly in NCJLFETs. Figure 2c is a comparison of the transfer characteristics of NC-JLFET and JLFETs. It is obvious that  $I_{\rm OFF}$  is significantly reduced for NC-JLFETs, which leads to the result that the switching characteristic becomes steeper because of the voltage amplifi-

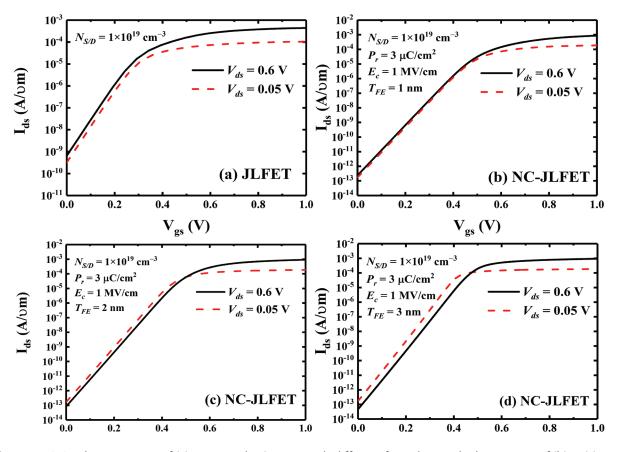

**Figure. 4:** DIBL characteristics of (a) JLFET and NC-JLFET with different ferroelectric thicknesses  $T_{FE}$  of (b) 1, (c) 2, and (d) 3 nm.

cation contributed by the ferroelectric layer. As shown in Fig. 2d, the on/off current ratio  $(I_{ON}/I_{OFF})$  of JLFETs increases with increasing  $N_{S/D}$  because increased  $N_{S/D}$ reduces the resistance of the source and drain, which increases the drive current. This trend is also in line with the conclusions obtained in [16,22]. However, for NC-JLFETs, the  $I_{ON}/I_{OFF}$  decreases as  $N_{S/D}$  increases. This is because increased  $N_{S/D}$  values induce doping-dependent electron mobility degradation [14]. Moreover, as the source and drain doping concentrations increase but the channel concentration remains constant, the  $I_{ON}/I_{OFF}$  values do not change much. When  $N_{S/D} = 5 \times 10^{19}$ cm<sup>-3</sup>, the  $I_{ON}/I_{OFF}$  value of the NC-JLFET is still larger than in the JLFET by a factor of nearly 10<sup>3</sup>.

Figure 3 gives the SS values of the JLFET and NC-JLFET for different  $N_{S/D}$  values. The SS in JLFET increases slowly with increasing  $N_{S/D'}$  but, in the NC-JLFET, SS shows a downward trend and all are below 60 mV/dec. These two phenomena can be explained by the following two equations:

$$SS = ln 10 \frac{kT}{q} \left( 1 + \frac{C_{\rm dm}}{C_{\rm ox}} \right) \approx 60 \times \left( 1 + \frac{C_{\rm dm}}{C_{\rm ox}} \right)$$

(3)

$$SS = 60 \times \left( I + \frac{C_{\rm dm}}{C_{\rm ox}} - \frac{C_{\rm dm}}{|C_{\rm FE}|} \right) \tag{4}$$

where  $C_{ox}$  is the gate oxide capacitance and  $C_{dm}$  is the depletion capacitance. As is well known, in JLFETs, the higher the doping concentration, the larger the  $C_{dm'}$  and therefore the larger the SS. In contrast, in NC-JLFETs, the larger the  $C_{dm'}$ , the greater the increase of  $C_{dm'}/|C_{FE}|$  compared with the increase of  $C_{dm'}/C_{ox'}$ , so the smaller the SS will be, that is, less than 60 mV/dec. This is the same as the change trend of SS caused by different doping concentrations of NC-JLGAAFET in [14].

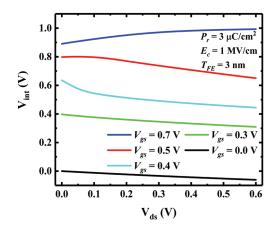

**Figure. 5:** Gate internal voltage ( $V_{int}$ ) versus drain voltage ( $V_{ds}$ ) for NC-JLFET with  $T_{FE} = 3$  nm.

For conventional JLFETs, when the drain voltage  $(V_{ds})$  increases, the source-drain depletion layer width is close to the channel length, which reduces the source barrier height. The decrease of the barrier height allows the source electrons to easily cross the barrier to reach the drain, and the channel charge controlled by the gate voltage is reduced, which leads to increased leakage current and lowered threshold voltage. This mechanism is known as the DIBL effect. For traditional JLFETs, increasing  $V_{ds}$  will tend to increase current ( $I_{ds}$ ), as can be seen in Fig. 4a. However, for NC-JLFETs, the relationship between the  $V_{ds}$  and  $V_{int}$  is:

$$V_{\rm int} = V_{\rm gs} - V_{\rm FE} = V_{\rm gs} + \left| V_{\rm FE} \right| \tag{5}$$

where  $V_{\text{FE}}$  is the voltage across the ferroelectric. Owing to drain and channel coupling, when  $V_{\text{ds}}$  increases, the gate charge decreases, which results in a decrease in  $V_{\text{FE}}$ . In addition, the  $V_{\text{int}}$  will also decrease, as shown in Fig. 5, which will definitely reduce the channel current intensity. Figures 4b, c, and d show the DIBL characteristics of the NC-JLFET with different  $T_{\text{FF}}$  values, and it

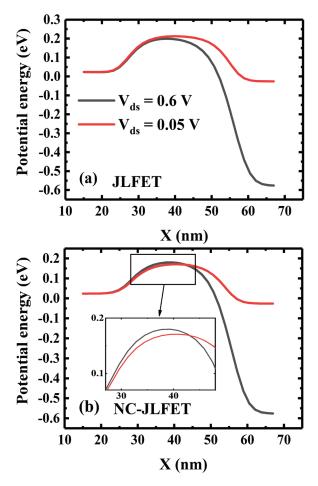

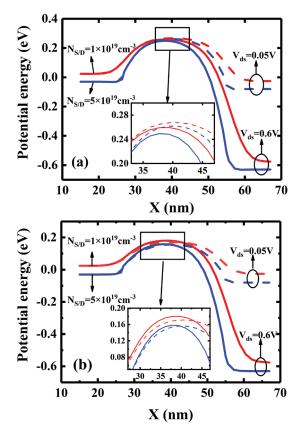

**Figure. 6:** Potential profile at high and low drain voltages ( $V_{ds}$ ). Applied voltage of  $V_{gs} = 0.3$  V. (a) JLFET and (b) NC-JLFET at  $T_{FF} = 3$  nm.

can be clearly seen that negative DIBL characteristics appear when  $T_{rf}$  = 2nm and 3 nm.

At the same time, negative DIBL can also be proved by comparing the potential distribution in the channel region of JLFETs and NC-JLFETs as shown in Fig. 6. For a traditional JLFET, the potential barrier height will decrease with increasing  $V_{ds}$ . For an NC-JLFET, the opposite trend is shown in Fig. 6b. That is, with increasing  $V_{ds'}$  the height of the barrier near the source will increase causing the negative DIBL phenomenon.

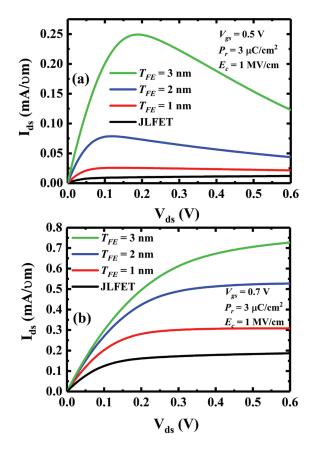

Figure 7 shows the  $I_{ds}$ - $V_{ds}$  output characteristic of NC-JLFET for different  $T_{FE}$  values at  $V_{gs} = 0.5-0.7$  V. As mentioned earlier, when  $V_{ds}$  increases,  $V_{int}$  decreases, which reduces the drain current. This exhibits a negative differential-resistance (NDR) characteristic as depicted in Fig. 7a. When  $V_{gs} = 0.5$  V,  $I_{ds}$  and  $V_{ds}$  have a positive correlation in the linear region. As  $V_{ds}$  continues to increase,  $I_{ds}$  decreases. This NDR effect can also be seen

**Figure. 7:** Output characteristics of NC-JLFET for different values of  $T_{FE}$  at (a)  $V_{gs}$  = 0.5 V showing NDR and (b)  $V_{gs}$  = 0.7 V showing saturation in the ON current.

in the relationship between  $V_{int}$  and  $V_{ds}$  shown in Fig. 5. However, when  $V_{gs} = 0.7$  V, only a positive correlation exists between  $V_{int}$  and  $V_{ds'}$  so the NDR effect will not appear [see Fig. 7b]. In addition, as the negative DIBL is related to  $C_{\text{FE'}}$  the NDR can be controlled by changing  $T_{\text{FE'}}$ . Despite the NDR, an NC-JLFET still provides a larger current than a traditional JLFET. It is worth mentioning that the simulation results of negative DIBL and NDR in our research are consistent with the results of [18].

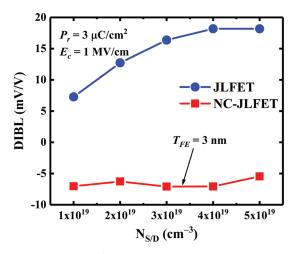

Figure 8 shows the DIBL values of a JLFET and NC-JLFET for different  $N_{s/D}$ . It can be clearly seen that as  $N_{s/D}$  increases the DIBL effect becomes more serious for the JLFET. This can also be seen in the potential profile diagram. It can be observed from Fig. 9a that the barrier height is significantly reduced when  $N_{s/D} = 5 \times 10^{19} \text{ cm}^{-3}$ , resulting in a more serious DIBL effect. However, for the NC-JLFET, increasing  $N_{s/D}$  has little impact on its DIBL, which can also be observed in the potential profile diagram. Figure 9b also shows that  $N_{s/D}$  increased from 1  $\times 10^{19}$  to 5  $\times 10^{19}$  cm<sup>-3</sup> and the barrier height shows a downward trend. Due to the negative capacitance effect, the negative DIBL phenomenon still occurs.

**Figure. 8:** DIBL of JLFET and NC-JLFET varying with source and drain doping concentration ( $N_{cro}$ ).

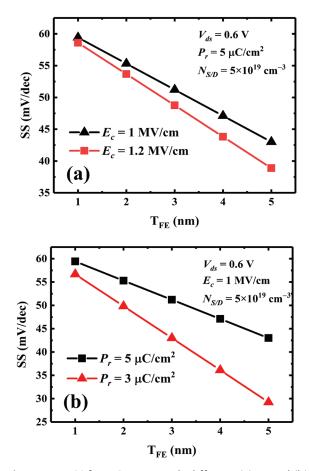

Figure 10 exhibits the effect of ferroelectric thickness  $(T_{FE})$  on SS for different ferroelectric material parameters ( $E_c$  and  $P_r$ ). It can be clearly seen that SS decreases with increasing  $T_{FE}$ . This is mainly because as  $T_{FE}$  increases,  $C_{FE}$  will decrease, which will make  $C_{MOS}$  more closely match  $C_{FF}$ :

$$C_{\rm FE} = \frac{dQ}{dV_{\rm FE}} \approx \frac{1}{2\alpha T_{\rm FE}} = \frac{2}{3\sqrt{3}} \frac{P_{\rm r}}{E_{\rm c} T_{\rm FE}}$$

(6)

$$A_{\rm G} = \frac{|C_{\rm FE}|}{|C_{\rm FE}| - C_{\rm MOS}} \tag{7}$$

$$SS = 60 \times (1 + \frac{C_{\rm dm}}{C_{\rm ox}}) \times \frac{1}{A_{\rm G}}$$

(8)

**Figure. 9:** Potential profile for different  $N_{\text{S/D}}$ . Applied voltage of  $V_{\text{gs}} = 0.3$ V. (a) JLFET and (b) NC-JLFET at  $T_{\text{FE}} = 3$  nm.

According to Eq. 7 [23], the voltage amplification factor  $(A_{\rm G})$  increases due to the improved matching between the  $C_{\rm MOS}$  and  $C_{\rm FE}$  ( $|C_{\rm FE}| - C_{\rm MOS} > 0$ ). The relationship between  $A_{\rm G}$  and SS is obtained by Eq. 8 [24],  $A_{\rm G}$  and SS have a negative correlation, so SS decreases with increasing  $T_{\rm FE}$ . The relationship between the ferroelectric capacitance  $(C_{\rm FE})$  and the ferroelectric material parameters ( $E_c$  and  $P_r$ ) is shown in Eq. 6 [11]. When  $P_r$  ( $E_c$ ) and  $T_{\rm FE}$  remain unchanged,  $C_{\rm FE}$  decreases as  $E_c$  increases ( $P_r$  decreases), and results in lower SS. The results obtained in the simulation also conform to this rule, as shown in Fig. 10a and b.

### 4 Conclusions

The electrical performance of a negative-capacitance double-gate junctionless transistor with additional source-drain doping determined by simulation analyses is presented in this paper. It was observed that the negative-capacitance effect and additional source-drain doping can increase the gate voltage and depletion capacitance, respectively, which makes the proposed NC-JLFET have higher  $I_{ON}/I_{OFF}$  and lower SS values. Then, the NDR and negative DIBL phenomenon are explained through the relationship between inter-

**Figure. 10:** SS for NC-JLFET with different (a)  $E_c$  and (b)  $P_r$  values for different ferroelectric thicknesses ( $T_{FF}$ ).

nal voltage and gate voltage. In addition, the influence of ferroelectric parameters on the NC-JLFET with additional source-drain doping is explored and shown to have better performance when the proper coercive field, remnant polarization, and ferroelectric thickness are chosen. The additional source-drain doped NC-JLFET studied can achieve superior performance and meet the requirements of low-power IC applications in the future.

# 5 Acknowledgments

This work is supported by Zhejiang Provincial Natural Science Foundation of China (Grant No. LY18F040005), and National Natural Science Foundation of China (Grant No. 61571171, 62071160).

# 6 Conflict of Interest

The authors declare no conflict of interest. The founding sponsors had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, and in the decision to publish the results.

# 7 References

- 1. E. Ko, J. Shin and C. Shin, "Steep switching devices for low power applications: negative differential capacitance/resistance field effect transistors." *Nano Convergence*, Vol. 5, no. 2, pp. 1-9, 2018. <u>https://doi.org/10.1186/s40580-018-0135-4</u>

- C. Lee, A. Afzalian, N. D. Akhavan, R. Yan, L. Ferain and J. Colinge, "Junctionless multigate field-effect transistor." *Appl. Phys. Lett*, Vol. 94, no. 5, pp. 053511, 2009. <u>https://doi.org/10.1063/1.3079411</u>

- J. Colinge, C. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A. Kelleher, B. McCarthy and R. Murphy, "Nanowire transistors without junctions." *Nat. Nanotechnol*, Vol. 5, no. 3, pp. 225-229, 2010. <u>https://doi.org/10.1038/nnano.2010.15</u>

- 4. S. Salahuddin, S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices." *Nano Lett*, Vol. 8, no. 2, pp. 405-410, 2008.

https://doi.org/10.1021/nl071804g

5. A. M. lonescu, "Negative capacitance gives a positive boost." *Nat. Nanotechnol,* Vol. 13, no. 1, pp. 7-8, 2018.

https://doi.org/10.1038/s41565-017-0046-2

V. Kumari, A. Kumar, M. Saxena and M. Gupta, "Study of Gaussian Doped Double Gate Junction-Less (GD-DG-JL) transistor including source drain depletion length: Model for sub-threshold behavior." *Superlattices Microstruct*, Vol. 113, pp. 57-70, 2017.

https://doi.org/10.1016/j.spmi.2017.09.049

C. Jiang, R. Liang, J. Wang and J. Xu, "Simulationbased study of negative capacitance double-gate junctionless transistors with ferroelectric gate dielectric." *Solid-State Electron*, Vol. 126, pp. 130-135, 2016.

https://doi.org/10.1016/j.sse.2016.09.001

N. M. Hossain, S. Quader, A. B. Siddik and M. I. B. Chowdhury, "TCAD based performance analysis of junctionless cylindrical double gate all around FET up to 5nm technology node." in 20th International Conference of Computer and Information Technology (ICCIT), 2017.

https://doi.org/10.1109/iccitechn.2017.8281858

9. H. Y. Yu, C. Ren, Y. Yeo, J. F. Kang, X. P. Wang, H. H. H. Ma, M. F. Li, D. S. H. Chan and D. L. Kwong, "Fermi pinning-induced thermal instability of metalgate work functions." *IEEE Electron Device Lett*, Vol. 25, no. 5, pp. 337-339, 2004. https://doi.org/10.1109/LED.2004.827643

- C. W. Yeung, A. I. Khan, A. Sarker, S. Salahuddin and C. Hu, "Low power negative capacitance FETs for future quantum-well body technology." in *International Symposium on VLSI Technology, Systems and Application (VLSI-TSA)*, 2013, pp. 1-2. https://doi.org/10.1109/VLSI-TSA.2013.6545648

- 11. C. Lin, A. I. Khan, S. Salahuddin and C. Hu, "Effects of the Variation of Ferroelectric Properties on Negative Capacitance FET Characteristics." *IEEE Trans. Electron Devices*, Vol. 63, no. 5, pp. 2197-2199, 2016.

https://doi.org/10.1109/TED.2016.2514783

T. Yu, W. Lü, Z. Zhao, P. Si and K. Zhang, "Effect of different capacitance matching on negative capacitance FDSOI transistors." *Microelectron. J*, Vol. 98, pp. 104730, 2020.

<u>https://doi.org/10.1016/j.mejo.2020.104730</u>

- P. Si, K. Zhang, T. Yu, Z. Zhao and W. Lü, "Analog / Radio-Frequency Performance Analysis of Nanometer Negative Capacitance Fully Depleted Silicon-On-Insulator Transistors." INFORM MIDEM, Vol. 50, no. 1, pp. 47-53, 2020. https://doi.org/10.33180/InfMIDEM2020.105

- Y. Choi, Y. Hong and C. Shin, "Device design guideline for junctionless gate-all-around nanowire negative-capacitance FET with HfO2-based ferroelectric gate stack." *Semicond. Sci. Technol*, Vol. 35, no. 1, pp. 015011, 2020. https://doi.org/10.1088/1361-6641/ab5775

- D. Moon, S. Choi, J. P. Duarte and Y. Choi, "Investigation of Silicon Nanowire Gate-All-Around Junctionless Transistors Built on a Bulk Substrate." *IEEE Trans. Electron Devices*, Vol. 60, no. 4, pp. 1355-1360, 2013.

https://doi.org/10.1109/TED.2013.2247763

- C. Lee, I. Ferain, A. Afzalian, R. Yan, N. D. Akhavan, P. Razavi, J. Colinge, "Performance estimation of junctionless multigate transistors." *Solid-State Electron*, Vol. 54, no. 2, pp. 97-103, 2010. <u>https://doi.org/10.1016/j.sse.2009.12.003</u>

- 17. L. Tu, X. Wang, J. Wang, X. Meng and J. Chu, "Ferroelectric Negative Capacitance Field Effect Transistor." *Adv. Electron. Mater*, Vol. 4, no. 11, pp. 1800231, 2018.

https://doi.org/10.1002/aelm.201800231

- S. Gupta, M. Steiner, A. Aziz, V. Narayanan, S. Datta and S. K. Gupta, "Device-Circuit Analysis of Ferroelectric FETs for Low-Power Logic." *IEEE Trans. Electron Devices*, Vol. 64, no. 8, pp. 3092-3100, 2017. <u>https://doi.org/10.1109/TED.2017.2717929</u>

- 19. Guide, Sentaurus Device User, and G. Version. "Synopsys." Inc., Sep (2017).

- M. Kao, Y. Lin, H. Agarwal, Y. Liao, P. Kushwaha, A. Dasgupta, S. Salahuddin and C. Hu, "Optimization of NCFET by Matching Dielectric and Ferroelectric Nonuniformly Along the Channel." *IEEE Electron Device Lett*, Vol. 40, no. 5, pp. 822-825, 2019. https://doi.org/10.1109/LED.2019.2906314

- M. H. Park, Y. H. Lee, H. J. Kim, Y. J. Kim, T. Moon, K. D. Kim, J. Müller, A. Kersch, U. Schroeder, T. Mikolajick and C. S. Hwang, "Ferroelectricity and Antiferroelectricity of Doped Thin HfO2-Based Films." *Adv. Mater*, Vol. 27, no. 11, pp. 1811-1831, 2015. <u>https://doi.org/10.1002/adma.201404531</u>

- N. Trivedi, M. Kumar, M. Gupta, S. Haldar, S. S. Deswal and R. S. Gupta, "Investigation of Analog/ RF performance of High-k Spacer Junctionless Accumulation-Mode Cylindrical Gate All Around (JLAM-CGAA) MOSFET." IEEE Uttar Pradesh Section International Conference on Electrical, Computer and Electronics Engineering (UPCON), 2016. <u>https://10.1109/UPCON.2016.7894652</u>23.

C. W. Yeung, A. I. Khan, S. Salahuddin and C. Hu, "Device design considerations for ultra-thin body non-hysteretic negative capacitance FETs." in *Third Berkeley Symposium on Energy Efficient Electronic Systems (E3S)*, 2013.

https://doi.org/10.1109/E3S.2013.6705876

B. Awadhiya, P. N. Kondekar, A. D. Meshram, "Effect of Ferroelectric Thickness Variation in Undoped HfO 2 -Based Negative-Capacitance Field-Effect Transistor." *J. Electron. Mater*, Vol. 48, no. 10, pp. 6762-6770, 2019. https://doi.org/10.1007/s11664-019-07483-1

Copyright © 2020 by the Authors. This is an open access article distributed under the Creative Com-

mons Attribution (CC BY) License (https://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Arrived: 04. 06. 2020 Accepted: 28. 08. 2020